cr1901 wrote:

I think the First Steps phase has at last ended after a year. Though I didn't have much to show for it, I still learned some valuable lessons from having my ideas (constructively) scrutinized. I think the most important thing I learned, even though it's emphasized over and over and over on this site is:

My initial goals were too much and that I needed to make tradeoffs. I wish I could put everything and the kitchen sink onto my SBC, and make it all discrete logic/building-friendly, but without PALs/CPLDs/level shifters and friends, I can only do so much.

I scaled back my project to the following goals:

- Use 65816 processor. Consider a 6502 build later.

- Just get something working first. Worry about ISA interfacing later (R1). This will be R0.

- Design for theoretical operation at at least 10MHz. Higher is better. 14MHz may be possible (I'll discuss later).

- Use parts that are still made.

- Use discrete components and TTL glue logic (I think I found a setup where 14MHz operation is possible with discrete TTL).

- Bank 0 should be distinguished, so that other banks can be used for extra RAM.

The plan is to build for 8MHz on veroboard using soldering (I have no provisions for wire wrap right now) or maybe lower speed- depends what TTL parts I have on hand. For theoretical operation, I've went through the trouble of calculating propogation delays, and trying to reduce the delays for the slowest parts (EPROM). To that end, I am using the

linked Python program. The Python program's variables should be self-explanatory, but it attempts to calculate the propagation delay from PHI2's falling edge to the time the EPROM is selected, and returns the maximum access time that satisfies the circuit so that data is out 10ns before PHI2's falling edge.

Memory Map is as follows (ROM split is deliberate- it's not important why, so don't ask):

|0x0000-0x3FFF|RAM|

|0x4000-0x7FFF|PRG ROM (Extra Forth words, helper routines, etc)|

|0x8000-0xBFFF|IO (VIA, ACIA, maybe PIA in future)|

|0xC000-0xFFFF|SYSTEM ROM|

|0x10000+|Extra RAM/ROM (future expansion)|

The program/schematic makes the following assumptions

- RWB is NOT gated for EPROM access (so attempt to write to ROM addresses will cause contention).

- BA0-7 to 373 setup time is not violated (it is neglible for ACT/ABT anyway).

- Delay from 373 output to Output Enable is longer than VDA/VPA to Output Enable.

The parts I used are the following (some are available in ABT variants), taken from search datasheets on Mouser:

|Connection |TTL Chip |Prop Delay (ns)|

|:------------------|:--------- |:--------------|

|BA0-7 to A16-23 |74ACT373N |10.4|

|BA0-7 to D0-7 |74ACT245N |9|

|A16-23 to BANK_ZERO|74ACT11030|8.1|

|Many |SN74ACT00N |8.5|

And lastly, I have attached the schematic of my current setup for EPROM accesses. First image is the CPU sheet, second is the EPROM and RAM sheet (ignore the RAM portion- it is wrong). The circuit below satisfies the A16-23 to ~OE conditions from my program for 8MHz, since:

8.1ns (8-input NAND) + 8.5ns (NAND) is < 33.6 ns.

VDA/VPA is also satisfied, as relative to PHI2's falling edge,

30ns address setup + 10ns data setup + 17ns OR (two NANDs) + 8.5ns = 65.5ns, which is less than 125ns-15ns = 115 ns for 8 MHz. I'll add that to my program later.

Code:

F:\Legacy\6502\SOURCE\R1\src>r1timing.py

Desired 65816 frequency (MHz): 8

Decoding delay from A0-A15 to ~CE (ns): 8.5

Required EPROM speed w/ 8.5 glue logic (max access time): 76.5

Decoding delay from A16-23 to ~OE: 33.6

Required bank 0x1-0xFF RAM/EPROM speed w/o glue logic: 33.6

CPU sheet:

Attachment:

The attachment r1_cpu.png is no longer available

EPROM glue sheet:

Attachment:

The attachment r1_eprom.PNG is no longer available

Does anyone who has dealt with higher speeds think I'm on the right track?

Hi

I see you mentioned you do not intend to use pld's etc.. But i was on the same track as you (at one point .. and found that gle logic and descrete ic interface make a mess of the whole circuit.. jus think of pld's as black functional boxes that have set of inputs and set of desired outputs .. then the glue logic functions are the combinatorial command you give to the pld takes bit of getting used too ..have a look at my page on mini SYM board

https://sites.google.com/site/gogleoops ... 2-mini-sbcand part of the code for memory mapping

field ioaddr= [a15..9];

cs6532_eqn = ioaddr:[A4XX..A7XX];

csrom_eqn = (ioaddr:[80XX..8FXX])#(ioaddr:[F0XX..FFXX]) ;

csram_eqn = (ioaddr:[00XX..07XX]) ;

for yours

|0x0000-0x3FFF|RAM|

|0x4000-0x7FFF|PRG ROM (Extra Forth words, helper routines, etc)|

|0x8000-0xBFFF|IO (VIA, ACIA, maybe PIA in future)|

|0xC000-0xFFFF|SYSTEM ROM|

|0x10000+|Extra RAM/ROM (future expansion)|

it be something like this

csram_eqn = (ioaddr:[00XX..3FXX]) ;

csrom_eqn = (ioaddr:[40XX..7FXX]) ;

csrvia_eqn = (ioaddr:[80XX..BFXX]) ;

cssysram_eqn = (ioaddr:[C0XX..FFXX]) ;

so you only need 8 address lines as input and 4 as output (which is your cs lines)

Only One 24pin slim Ic and all your logic gates IC's disappear

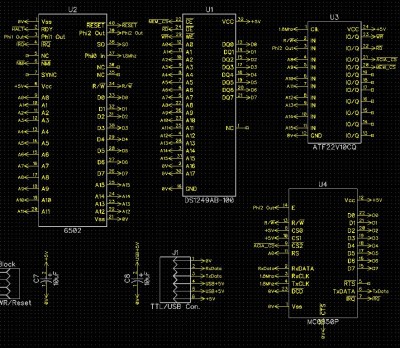

As an example I am doing a similar 6502 setup ..with no glue logic and even with no separate ram/rom but NVram that simplifies design even further ..In fact if you use the DS1249 (2Mbit NvRAM)

it will give you extra ram as you need. The only issue with nvram is programming it and then making sure the "rom" areas do not get over written as you would have to program them again.

I think the solution is to not enable the WR signal to the ram when it is accidentally dealing with rom address area. .. and that you can deal with through the pld and no extra logic

see pic below

Attachment:

6502ver2.JPG [ 271.04 KiB | Viewed 1410 times ]

6502ver2.JPG [ 271.04 KiB | Viewed 1410 times ]

applogiz for spelling ..bit I am a bitt dilexic