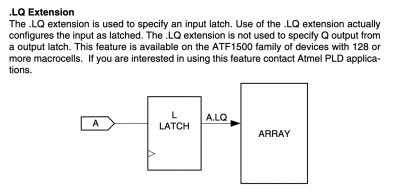

Hello! I've been trying to use the .LQ extension in WinCUPL to define an input latch for my '816 bank address. According to Atmel's WinCUPL User's Manual:

Attachment:

Screenshot 2023-06-26 at 23.56.53.png [ 95.56 KiB | Viewed 4073 times ]

Screenshot 2023-06-26 at 23.56.53.png [ 95.56 KiB | Viewed 4073 times ]

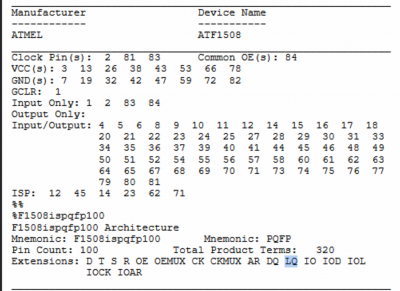

According to the Devhelp.pdf file in WinCUPL's installation, my ATF1508 indeed supports this extension:

Attachment:

Screenshot 2023-06-26 at 23.56.10.png [ 290.72 KiB | Viewed 4073 times ]

Screenshot 2023-06-26 at 23.56.10.png [ 290.72 KiB | Viewed 4073 times ]

However, I haven't found any examples showing how to configure this latch, specifically its clock. I've tried the following (also with .IOCK and .CKMUX for good measure), which results in the fitter not producing any output / crashing.

Code:

PIN 1 = CLK ;

PIN = [DBA0..7];

PIN = [A16..23];

[A16..23] = [DBA0..7].LQ;

[DBA0..7].CK = CLK;

Here is the output from the fitter

Code:

Atmel ATF1508AS Fitter Version 1.8.7.8 ,running Tue Jun 27 00:03:46 2023

fit1508 C:\WINCUPL\WINCUPL\BB816.tt2 -CUPL -dev P1508C84 -JTAG ON

****** Initial fitting strategy and property ******

Pla_in_file = BB816.tt2

Pla_out_file = BB816.tt3

Jedec_file = BB816.jed

Vector_file = BB816.tmv

verilog_file = BB816.vt

Time_file =

Log_file = BB816.fit

err_file =

Device_name = PLCC84

Module_name =

Package_type = PLCC

Preassign_file =

Property_file =

Sleep_mode =

Preassignment =

Security_mode = OFF

Pin_keep_mode = ON

Dedicated_input_clock =

Dedicated_input_reset =

Dedicated_input_oe =

supporter = CUPL

optimize = ON

Soft_buffer =

Xor_synthesis = OFF

Foldback_logic = on

Expander =

Cascade_logic = OFF

Dedicated_input =

Output_fast = OFF

*******************************

Power down pin 1 = OFF

Power down pin 2 = OFF

power_reset = OFF

JTAG = ON

TDI pullup = ON

TMS pullup = ON

MC_power = OFF

Open_collector = OFF

ITD0 = ON

ITD1 = ON

ITD2 = ON

Fast_inlatch = off

*******************************

Replacing the two lines with only "[A16..23] = [DBA0..7];" gives me an output in the fitter, so I'm pretty sure this extension is the problem.

Has anyone looked into this before? I'm worried about the "Contact Atmel PLD applications" prompt, if it means you need some special incantation to use the functionality.