hmmm, i would personally always put PLCC and DIP chips in sockets, regardless of if you actually plan on taking them out again or not.

simply having the option to take them out without doing any desoldering is always nice to have.

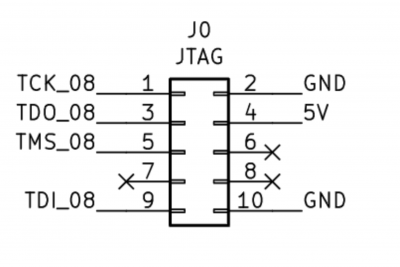

but as Ed said, JTAG is designed for in-system programming, so you program the CPLD/FPGA while it's in your system using an onboard JTAG header.

said header has a standardized pinout, for the AT150x series of CPLDs it's this:

Attachment:

chrome_6lFAUuT1ot.png [ 266.26 KiB | Viewed 8772 times ]

chrome_6lFAUuT1ot.png [ 266.26 KiB | Viewed 8772 times ]

also make sure to never use the JATG Pins for your logic, as that will disable JTAG. which casues some headaches!

also in regards to the voltage, 5V FPGAs pretty much don't exist (technically they do, but are too expensive to be worth it). but if you really want to use an FPGA, then you could design your whole system to run on 3.3V instead.

it shouldn't be that difficult, unless you plan on using some part that requires 5V signals, but even then you could connect that one using level shifters and have everything else still run at 3.3V.

though of course this is only really an option if you're planning a new system, and not when you already have one where you want to replace the existing logic with an FPGA.

Yuri wrote:

plus (I hope) something to shadow the ROM into a faster RAM chip and then have it switch the clock on boot.

hm, if you're using a 65c02 have you thought about making a simple RDY circuit to slow the CPU down when accessing the ROM?

obviously you lose some performance, but it seems much easier to implement. plus later on you can then go back and redo that logic to allow the CPU to disable the ROM (which then also disabled the RDY circuit).

Yuri wrote:

I'll check that out WinCupl is clearly a bit dated and has some.... ah.... "personality" let's say.

i found that using the commandline CUPL program directly works better.

alternatively you can use Verilog/VHDL with Quartus II web edition v13.0.

make your project around the MAX7000 series:

MAX7032 = ATF1502

MAX7064 = ATF1504

MAX7128 = ATF1508

then after synthesizing, use POF2JED to... well convert the .pof file from Quartus to a .jed file to program into the CPLD

it's a bit of a process, but i've been using it for years now and it works well enough.

but this sadly won't be an option if you're on Linux.