While moving a SST39SF010 flash from TL866 programmer to CPLD6502

trainer, I inadvertently inserted the chip backward and damaged the flash. This incident makes me think about an in-situ flash programmer as the first project of CPLD6502. In-situ programming means the flash can be reprogrammed without removing from its socket; furthermore, a blank flash can be programmed from scratch. This is not meant to be a general purpose flash programmer. I just want it to program the inexpensive Microchip SST39SF0x0.

The features of an in-situ flash programmer are:

* Two modes of operation, program mode and normal mode,

* Bootstrap from an internal

CPLD ROM in program mode,

* Load data to be programmed and associated algorithm externally,

* Able to write to flash's command registers to execute program command sequence

* Boot from freshly programmed flash in normal mode.

This will be a mult-session project. In this session I'll talk about the theory of operation as implemented in CPLD6502

trainer. Next session I'll describe the

CPLD design and ROM bootstrap program; the last session is on program loader, flash algorithm and data to be programmed.

Theory of operation of an in-situ flash programmer as implemented in CPLD6502 trainer.There will be two modes of operation. In normal mode, the CPLD6502 boots off the external flash located at $F000-$FFFF; in program mode, the CPLD6502 boots off an internal

CPLD ROM located at $F000-$FFFF while the external flash is a write-only device write accessible from $8000-$FFFF. Power cycling or reset is the only way to enter normal or program mode. No operator interaction needed (other than turn on the power) to boot in normal mode. To boot in program mode, the switch labelled "Single Step" need to be pressed and hold while power is applied.

The memory map of normal mode is as follow:

$F000-$FFFF, external flash read only.

$E000-$EFFF, I/O space, internal serial port is located at $E400-$E4FF

$0000-$DFFF, RAM, read and write.

The memory map of programming mode is as follow:

$F000-$FFFF, internal

CPLD ROM, read only

$E000-$EFFF, I/O space, internal serial port is located at $E400-$EFFF

$0000-$DFFF, RAM, read and write

Write access to $8000-$FFFF will shadow write to the external flash. The external flash is not read accessible.

The reason for shadow write of the external flash is because programming command sequence requires write access to registers at address x101 0101 0101 0101 and address 1010 1010 1010 1010. This corresponds to addresses $D555 and $AAAA. Higher order address bits are ignored. This is a common protocol for programming flash memories. Since flash is shadowed from $8000-$FFFF, up to 32K of flash can be programmed. However because the normal mode only uses 4K of flash from $F000-$FFFF, this programmer will only write top 4K of flash.

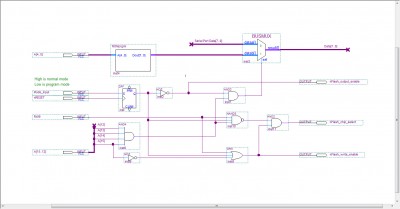

Attachment:

flash programmer block diagram.jpg [ 173.03 KiB | Viewed 7506 times ]

flash programmer block diagram.jpg [ 173.03 KiB | Viewed 7506 times ]

The block diagram above shows how mode influences the data path and controls of flash memory. Mode input is latched at the rising edge of nRESET. Mode latched low is the program mode that enables ROM data path in memory space $F000-$FFFF. Program mode also disables the active-low flash output enable. It also disables the active-low flash chip select unless it is a write to $8000-$FFFF.

If mode input is latched high, it is in normal mode where internal data path is disconnected from the ROM; the active-low flash output enable is always enabled; the active-low flash write enable is disabled, and the active-low flash chip select is enabled when reading memory area $F000-$FFFF.

In next session I'll describe the boot ROM and how the concept is implemented in

CPLD.

Bill