Quote:

Are you aware of Grant Searle's minimal designs?

http://searle.hostei.com/grant/Yes, Grant has some excellent designs.

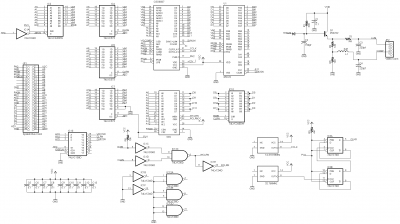

A C64-like computer was designed for a test rig. The system will be composed of a least two circuit boards. The free cad toolset is limited to boards that are 3” x 4” and everything won’t fit on one board. The boards will be connected with a 50-pin connector.

A 14.318MHz oscillator is used for the color clock. A 32.768MHz oscillator is divided by four to generate an 8.192 MHz dot clock signal. This signal is slightly off the required 8.182 MHz signal, but color output isn’t being used so this is probably okay. Otherwise it would be a pita to generate the 8.18MHz clock. The VIC-II chip generates the PHI02 clock for the system.

The board only uses the sync and luminance outputs of the VIC-II chip since a VGA replacement will be used. Composite video out is only needed to verify the circuit works with a 6567.

A 65C22 is used to supply the high order address lines for when the VIC-II has control of the bus.

Three transparent latches are used to latch the row and column address from the VIC-II to generate an address for the static RAM (on the cpu board).

All the parts are low power CMOS except for the 6567.

Attachment:

File comment: Video board for test computer

Test6567Sch.png [ 34.97 KiB | Viewed 7767 times ]

Test6567Sch.png [ 34.97 KiB | Viewed 7767 times ]