yzoer wrote:

The one thing I like about CPLD's is the fact that they don't have to be configured on boot. One thing to note though is that 'most' CPLD's only have a re-write span of 100 times or so.

Yes, the separate config flash, and delay time before the circuit is useable, are two disadvantages of FPGAs.

Quote:

With regards to the limited #of resources / pins, I actually see that as a challenge! Kinda like doing 3d code on a 6502! It's amazing how much you can do when you give it some though. I managed to put a VGA controller, DMA engine and all the glue logic (address decoding, registers etc) into a single EPM7128...

Ok, you have got my interest.

Are you willing/able to share any of this design? It sounds very impressive, for such a "limited" part. I'm assuming the Xilinx and Altera macrocells are comparable. Do you use VHDL, Verilog, Abel, or something else?

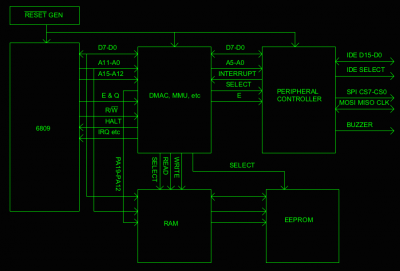

So I have been giving my next micro some more thought and have come up with this schema/block diagram, which I think is achievable with two 84 pin PLCC devices. It shows the major signals:

Attachment:

6809v2schema.png [ 42.07 KiB | Viewed 2296 times ]

6809v2schema.png [ 42.07 KiB | Viewed 2296 times ]

Though this is a 6809 computer, I think probably 95-99% of the design is in fact generic.

Hopefully you can make some sense of the diagram, though I admit that diagraming is not one of my strong points. Of course very little of this is implemented so far, nor have devices been properly chosen etc. Peripheral ICs (VIAs etc) are fairly obvious extensions of the memory devices, but with their own chip selects and interrupt lines.

PLD 1, the DMAC, MMU and core logic:

DMAC which will operate as a cycle stealer though HALT cycles. Arbitary addressing on the source and destination, as well as a (probably limited to 64KByte) length field. Will operate on physical addresses (I think). Optional increments on both source and destination. Interrupt generator when transfer is complete.

MMU. I think I described this quite completely in a previously post, so wont repeat it here.

Address decoding of the physical addresses. Memory map described later in this post.

READ and WRITE gated from E (clock) and R/W

Interrupt routing, for NMI, FIRQ, IRQ, with mask registers for all three, as well as a current status register (hopefully I won't need more then 8 interrupts)

RESET generation from /RESET (this is needed by the DUART)

Random glue logic for the AY sound IC, and VDC

PLD 2, the "peripheral controller":

Primitive IDE interface, such that a 16bit IDE device appears transparently as an 8 bit device (such that the DMA controller can pull of a disk block) - some details, like which lines need to be directly attached to the IDE port and which can come from the MPU bus, are a bit fuzzy

SPI interface - something like the awesome 65SPI (hopefully I can find the similar VHDL version and get it working)

Simple sounder interface

So the memory map. Fairly simple really. Physical address is 20 bits. Must admit I've not thought this through completely yet.

Code:

0x00000 - 0x7ffff : 512 KB RAM

0x80000 - 0x9ffff : DMAC/MMU registers

0xa0000 - 0xa002f : IDE/SPI/buzzer registers

0xf0000 - 0xf7fff : 32KB EEPROM

The MMU of course makes the physical address decoding fairly arbitrary, really. There will be one fixed page, at virtual address 0xf000 which will always map to 0xff000 so that the interrupt vectors are always available.

Pin requirements so far look like this:

PLD 1:

12 - address within page

4 - high virtual address

8 - high physical address

8 - databus

2 - clocks (may need only 1, if I don't find a use for Q)

1 - R/W

2 - READ and WRITE

2 - RESET and /RESET

3 - interrupt outputs

1 - halt output

2 - RAM and ROM chip selects

This makes about 45 pins, leaving around 15 for device selects and interrupt inputs. This should be just enough, though of course I can do decoding in another IC if necessary (but I really do not want to)

PLD 2:

1 - chip select

6 - address lines for registers

8 - databus

1 - clock

2 - READ and WRITE

1 - /RESET

1 - interrupt

16 - IDE databus

1 - IDE chip select

8 - SPI selects

3 - SPI MOSI, MISO, CLK

1 - buzzer output line

This makes about 50 lines, leaving some spare.

So the next choice is what PLDs to use. I think the MMU design will demand some fairly heavy logic, and RAM bits to hold the 16 by 8 page table. Probably the neatest thing to do is to use two EPF10K10 in PLCC84, hopefully with both of them programmed from a single EPC2.

If anyone has any suggestions for improvements, criticisms, etc of this very rough idea I would dearly love to hear about it.