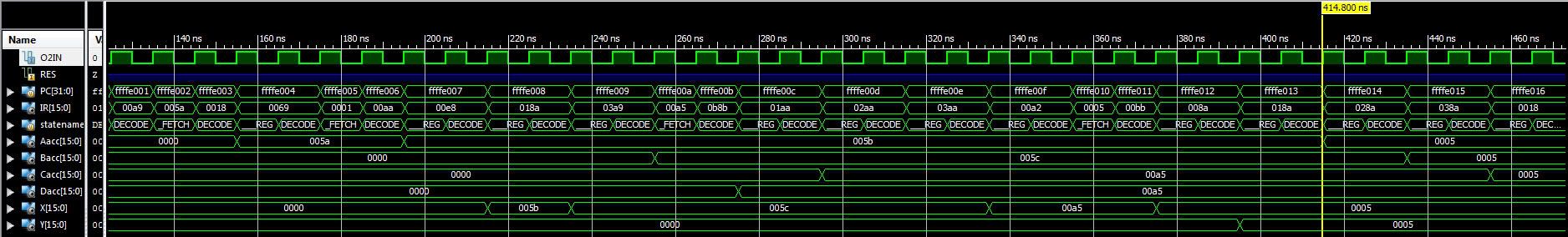

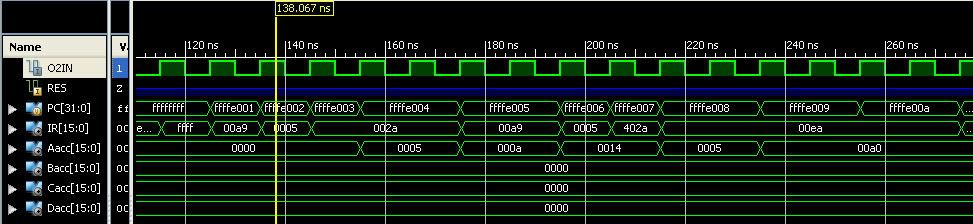

Proof is in the pudding. Here is the pudding!

Code:

START LDA #$5A ;00A9,005A

CLC ;0018

ADC #$01 ;0069,0001

TAX ;00AA

INX ;00E8

TXB ;018A

LDDi ;03A9

.BYTE $00A5 ;00A5

TDC ;OB8B

TBX ;01AA

TCX ;02AA

TDX ;03AA

LDX #$05 ;00A2,0005

TXY ;00BB

TXA ;008A

TXB ;018A

TXC ;028A

TXD ;038A

CLC ;0018

ADCDi ;0F69 Add op to D Acc, store in D Acc

.BYTE $0001 ;0001

ADCDopAi ;0369 Add op to D Acc, store in A Acc

.BYTE $000A ;000A

ADCAopBi ;0469 Add op to A Acc, store in B Acc

.BYTE $0001 ;0001

ADCBopCi ;0969 Add op to B Acc, store in C Acc

.BYTE $0002 ;0002

TCY ;02A8

TYX ;00AB

NOP

NOP

NOP

NOP

NOP

NOP

CLC ;0018

ADC #$01 ;0069,0001

TAX ;00AA

INX ;00E8

TXB ;018A

LDDi ;03A9

.BYTE $00A5 ;00A5

TDC ;OB8B

TBX ;01AA

TCX ;02AA

TDX ;03AA

LDX #$05 ;00A2,0005

TXY ;00BB

TXA ;008A

TXB ;018A

TXC ;028A

TXD ;038A

CLC ;0018

ADCDi ;0F69 Add op to D Acc, store in D Acc

.BYTE $0001 ;0001

ADCDopAi ;0369 Add op to D Acc, store in A Acc

.BYTE $000A ;000A

ADCAopBi ;0469 Add op to A Acc, store in B Acc

.BYTE $0001 ;0001

ADCBopCi ;0969 Add op to B Acc, store in C Acc

.BYTE $0002 ;0002

TCY ;02A8

TYX ;00AB

NOP

NOP

NOP

NOP

NOP

NOP