Ok, I believe I got it working!

For opcode bits [11:10] of ADC/SBC/AND/ORA/EOR the function I have looks like this:

Code:

[11:10] FUNCTION

0: 0 original ADC/SBC/AND/ORA/EOR on 4 Acc's (as defined by bits [9:8])

0: 1 add value in operand to A Acc and store in B Acc

1: 0 add value in operand to B Acc and store in C Acc

1: 1 add value in operand to C Acc and store in D Acc

0: 0 original ADC/SBC/AND/ORA/EOR on 4 Acc's (as defined by bits [9:8])

0: 1 add value in operand to A Acc and store in B Acc

1: 0 add value in operand to B Acc and store in C Acc

1: 1 add value in operand to C Acc and store in D Acc

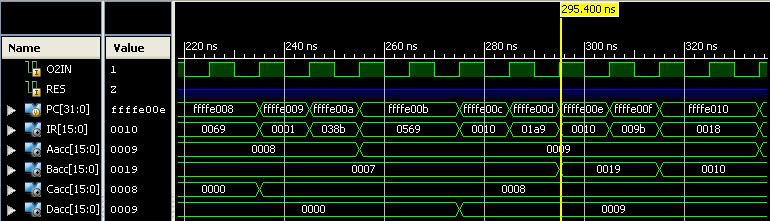

This small chunk of assembly is working in ISim:

Code:

$FFFFE0000 LDA #$07

TAB ;Transfer A Acc to B Acc

CLC

ADC #$01

TAC ;Transfer A Acc to C Acc

ADC #$01

TAD ;Transfer A Acc to D Acc

$FFFFE00B ADCAopBi ;Add op value to A Acc, store in B Acc

.BYTE $0010

LDBi ;LDB #$10

.BYTE $0010

TBA

CLC

--code trimmed here, due to waveform end--

TAB ;Transfer A Acc to B Acc

CLC

ADC #$01

TAC ;Transfer A Acc to C Acc

ADC #$01

TAD ;Transfer A Acc to D Acc

$FFFFE00B ADCAopBi ;Add op value to A Acc, store in B Acc

.BYTE $0010

LDBi ;LDB #$10

.BYTE $0010

TBA

CLC

--code trimmed here, due to waveform end--