Dr. Jekyll.

I really like your idea. I spent a lot of time adapting it to my project. First of all, I wanted to simplify it to fit into one GAL.

To start with, I chose the codes 02,22,42,62 as "safe", which means that in 6502 no one uses them

, and in 65c02 they are additional NOPs.

I noticed that to convert code 02 to 8e, 22-ae and 62-ea, you just need to set the d1, d2, d3, d7 bits appropriately and leave the d0, d4, d5 bits unchanged.

If, additionally, the presence of "new" STX LDX codes is signaled at the IO output, I will be able to access the normally hidden IO register. Interestingly, if I extend the IO signal for another PHI1 clock, the register can be 16-bit or 256 8-bit, and if I extend it for the duration of the instruction, I can theoretically get $FFFF of IO registers available in a separate space something like Z80.

Attachment:

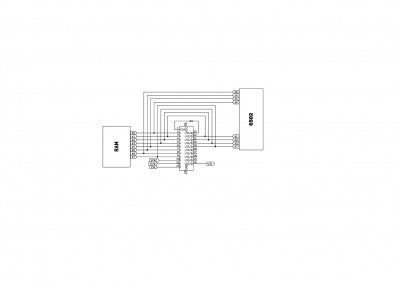

File comment: my proposal for a system that converts the JAM codes of the 6502 processor

GAL22V10

schemat3.jpg [ 59.95 KiB | Viewed 276 times ]

schemat3.jpg [ 59.95 KiB | Viewed 276 times ]